关于pcb线路板可靠性测试方法主要分为两个类型:分板级测试和芯片测试,板级测试又分无源测试,有源测试。板级测试的目的是验证在当前特定的线路板上,板材、拓扑结构、走线长度等等都已固化的情况下,信号质量如何。芯片测试的目的是验证这款芯片,它的各项性能最好能到什么程度、最薄弱的环节又在哪。因为芯片测试的仪器是误码仪,跟板级测试的手段、目的都不相同,所以今天UG环球先讲讲板级测试中的有源测试,芯片测试放到下次再讲。

关于pcb线路板可靠性测试问的最多的问题是"电路板测试的具体步骤、需要测试哪些参数、如何看懂波形及如何从波形上判断信号质量。”这个问题看似寥寥两行,其实是个范围非常大的问题。

不同的信号有不同的可靠性测试方法:比如接口测试,应先得有个test fixture,将板子上的信号引到fixture上,再用SMA cable或者probe进行测试,典型的有HDMI、USB、PCIE、 网口等,如果你是板内信号测试,那你就在板上的测试点上用probe进行点测。

其欺,不同的信号需要可靠性测试的参数不同:有的要测skew ,对间对内的skew都要测,典型就是各种显示接口,如HDMI ;有的要测波形、时序,像需要参考外部时钟采样的信号基本都要测,或I2C、DDR等,像I2C这种菊花链结构信号,总线上会挂多个device,每个device有自己唯一的地址代码,因此要根据地址代码把每个device都测到; 有的仅需测眼图即可,内嵌时钟信号的serdes信号都属于这种,好比PCIE ;有的要测板子工作时的极限情况,比如所有设备都插上同时工作时的电压跌落、插拔动作造成的浪涌,典型的就是USB ;有的要测试晶振出来时钟信号的频率及偏差,此时不能示波器测,要用频率计测(由于频率计的操作实在是太简单了,就不展开讲了) ;前面列举的”有...的”都是针对信号,电源除 了要分别测轻载、重载时的电源压降、纹波噪声,有时还要测power on、power off的时序。

从设计阶段简单介绍pcb线路板可靠性测试的过程!

设计线路板时要考虑到这根信号是否有可靠性测试需求,通常这个DFT ( Design ForTest )检查会放在设计基本完成时做。若有测试需求,检查在RX BGA端附近有没有过孔或AC耦合电容,有就不需要再额外添加可靠性测试点,以避免引入多余的东西: -个开窗的圆形焊盘.肯定比你的走线要宽得多,这对于信号来说会额外增加一一个阻抗不连续点。如果芯片直接表层出线且在芯片BGA焊盘500mil以内都没有“天然的”测试点,那就需要人工额外加测试点了,测试点的要求是:位置加在500mil以内,越近越好,圆形测试点的直径越小越好, -般20mil。

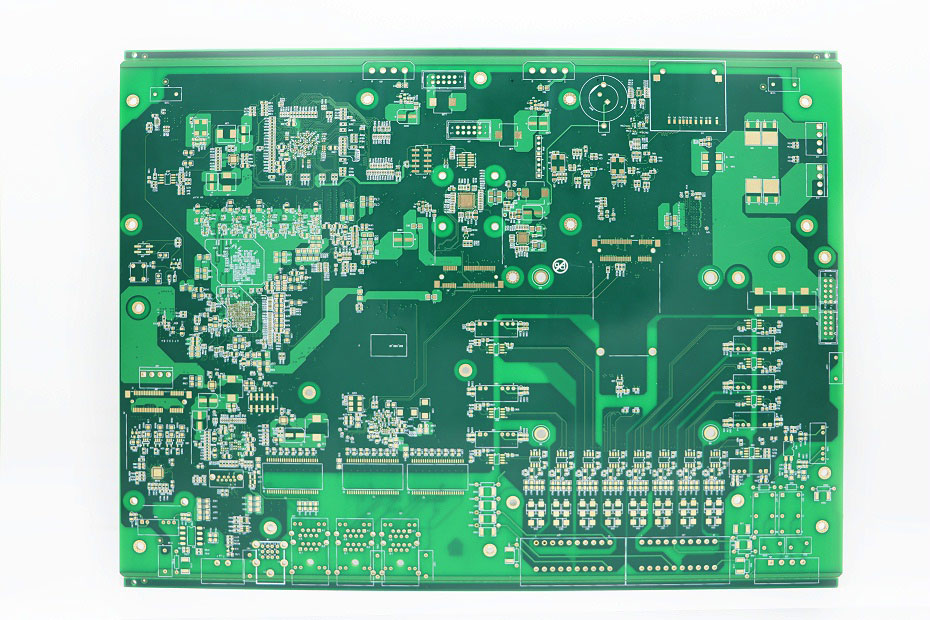

做好后的线路板工厂会用TDR做基本的阻抗测试,但板厂做的是阻抗条测试,不是你板上真正的链路。一般你会拿到- -两片光板,方便你自己做板内链路的阻抗测试,等PCBA贴片焊接完成后,线路板上电正常的才会拿去做SI测试。

以一个DDR4- 2400的地址信号测试为例简单介绍可靠性测试过程:先选一台带宽≥6GHz的示波器,加-根单端探棒、一根差分探棒 ;挑选最近、最远两个颗粒;单端、差分探棒分别点在赖粒端的地址、时钟信号上。

结果发现最近的颗粒上在400mV- 500mV间地址信号存在明显的回沟。功能测试也发现DDR4信号有误码,甚至都不能初始化。

回沟是由于颗粒感受到的阻抗不匹配造成的,因为DDR的地址信号大多数情况下都是一拖多的结构,每一个颗粒处在链路的不同位置,所以多重反射后每个颗粒感受的阻抗也是不一样的,调整了走线以使减弱阻抗不匹配的反射程度,调整后颗粒die.上所有的地址信号回沟都远离了VIL/VIH。