设计四层pcb打样是个非常考验人耐心的一份工作,特殊是一些多高层电路板设计,电路走线更是越发精密,对于四层pcb设计而言也不例外,那么UG环球在设计四层板时需要注意哪些基本要点呢!

1.元件封装的准备,尽量调用标准封装库中的文件; 严密按照所选期间的datasheet上的规范制作封装,不能忽略累积误差; 注意二极管、三极管等极性元件以及一些非对称元件的引脚定义不能搞错.

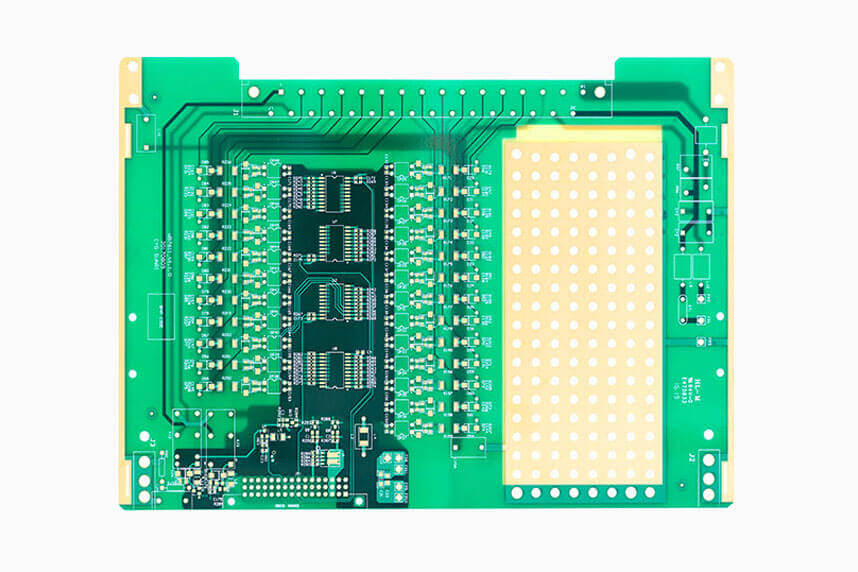

2.合理布局,尽量按照参考板的模式进行布局; 模块化布局; 要求模拟电路与数字电路分开; 输入模块和输出模块隔离; 去耦电容尽量靠近元件的电源/地; 电源等发热单元要考虑散热,主发热元件靠近出风口,大体积元件的放置避开风路; 元件分布均匀,避免电流过于密集; 板上的跳线或按键考虑易操作性; 元器件的排列尽量整齐美观; 考虑机械尺寸,不要超过结构所允许的范围。

3.PCB分层,如果有参考板,按照参考板进行分层; 多层板安排:顶层和底层为元件面,第二层为地平面,倒数第2层为power layer; 在不影响性能的情况下,减少PCB层数,降低成本。

4.电源考虑,系统电源入口做高频和低频滤波处理; 功率较高的器件配备大容量电容去除低频干扰; 每个器件配备0.1uF电容过滤高频干扰; 高频器件电源管脚和电容之间串连磁珠达到更好的效果; 去耦电容的引线不能过长,特别是高频旁路电路不能带引线。

5.时钟考虑,时钟电路要尽量靠近芯片; 晶体下方不要走线; 晶体外壳接地,增加抗电磁干扰能力; 频率大于200MHz的时钟信号有地线护送; 时钟线宽大于10mil; 时钟输出端串连22~220欧的阻尼电阻。

6.高速信号,采用手工布线; 高速总线走线尽量等长,并且在靠近数据输出端串联22~300欧的阻力电阻; 高速信号远离时钟芯片和晶体; 高速信号远离外部输入输出端口,或地线隔离。

7.差分信号,差分信号线要平行等长; 信号之间不能走其他信号线; 信号要求在同一层上。

8.走线规范,不同层的信号垂直走线; 地线和电源层不要走线,否则要保证平面的完整性; 导线宽度不要突变; 导线变向时倒角要大于90度; 定位孔周围0.5mm范围不要走线。 另外必须要完全通过PCB规则的DRC检查。